# Section 2. CPU for Devices with M4K® Core

# **HIGHLIGHTS**

This section of the manual contains the following topics:

| 2.1  | Introduction                                         | 2-2  |

|------|------------------------------------------------------|------|

| 2.2  | Architecture Overview                                | 2-3  |

| 2.3  | PIC32 CPU Details                                    | 2-6  |

| 2.4  | Special Considerations When Writing to CP0 Registers | 2-11 |

| 2.5  | Architecture Release 2 Details                       | 2-12 |

| 2.6  | Split CPU bus                                        | 2-12 |

| 2.7  | Internal System Busses                               | 2-13 |

| 2.8  | Set/Clear/Invert                                     | 2-13 |

| 2.9  | ALU Status Bits                                      | 2-14 |

| 2.10 | Interrupt and Exception Mechanism                    | 2-14 |

| 2.11 | Programming Model                                    | 2-14 |

| 2.12 | Coprocessor 0 (CP0) Registers                        |      |

| 2.13 | MIPS16e® Execution                                   | 2-55 |

| 2.14 | Memory Model                                         | 2-55 |

| 2.15 | CPU Instructions, Grouped By Function                | 2-56 |

| 2.16 | CPU Initialization                                   | 2-59 |

| 2.17 | Effects of a Reset                                   | 2-60 |

| 2.18 | Related Application Notes                            | 2-61 |

| 2.19 | Revision History                                     | 2-62 |

Note:

This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the "CPU" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

#### 2.1 INTRODUCTION

The PIC32 MCU is a complex system-on-chip (SoC) that is based on the M4K<sup>®</sup> Microprocessor core from MIPS<sup>®</sup> Technologies. The M4K<sup>®</sup> is a state-of-the-art, 32-bit, low-power, RISC processor core with the enhanced MIPS32<sup>®</sup> Release 2 Instruction Set Architecture (ISA).

This chapter provides an overview of the CPU features and system architecture of the PIC32 family of microcontrollers that are based on the  $M4K^{\textcircled{\$}}$  processor core.

## 2.1.1 Key Features

- Up to 1.5 DMIPS/MHz of performance

- Programmable prefetch cache memory to enhance execution from Flash memory (not available on all devices; refer to the specific device data sheet to determine availability)

- 16-bit Instruction mode (MIPS16e®) for compact code

- · Vectored interrupt controller with up to 96 interrupt sources

- · Programmable User and Kernel modes of operation

- Atomic bit manipulations on peripheral registers (Single cycle)

- Multiply-Divide unit with a maximum issue rate of one 32 x 16 multiply per clock

- High-speed Microchip ICD port with hardware-based non-intrusive data monitoring and application data streaming functions

- · EJTAG debug port allows extensive third party debug, programming and test tools support

- · Instruction controlled power management modes

- Five-stage pipelined instruction execution

- Internal code protection to help protect intellectual property

# 2.1.2 Related MIPS® Documentation

- MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core Software User's Manual MD00249-2B-M4K-SUM

- MIPS<sup>®</sup> Instruction Set MD00086-2B-MIPS32BIS-AFP

- MIPS16e<sup>®</sup> MD00076-2B-MIPS1632-AFP

- MIPS32<sup>®</sup> Privileged Resource Architecture MD00090-2B-MIPS32PRA-AFP

# 2.2 ARCHITECTURE OVERVIEW

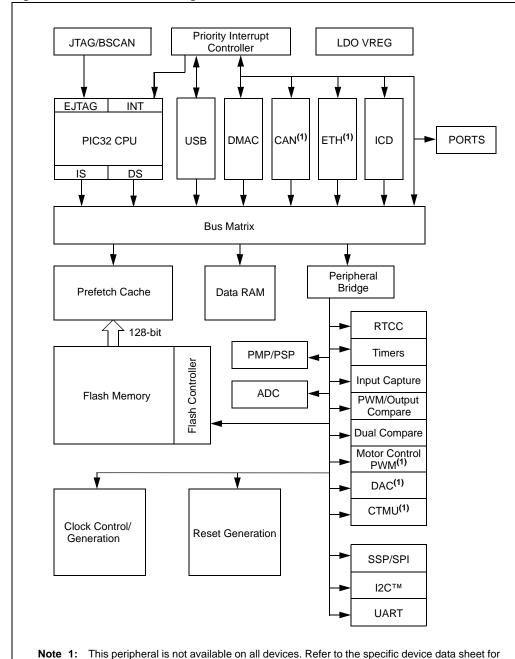

The PIC32 family of devices are complex systems-on-a-chip that contain many features. Included in all processors of the PIC32 family is a high-performance RISC CPU, which can be programmed in 32-bit and 16-bit modes, and even mixed modes. PIC32 devices contain a high-performance interrupt controller, DMA controller, USB controller, in-circuit debugger, high-performance switching matrix for high-speed data accesses to the peripherals, and on-chip data RAM memory that holds data and programs. The unique prefetch cache and prefetch buffer for the Flash memory, which hides the latency of the Flash, provides zero Wait state equivalent performance.

Figure 2-1: PIC32 Block Diagram

availability.

© 2007-2012 Microchip Technology Inc.

There are two internal busses in PIC32 devices for connection to all peripherals. The main peripheral bus connects most of the peripheral units to the bus matrix through a peripheral bridge. There is also a high-speed peripheral bridge that connects the interrupt controller, DMA controller, in-circuit debugger, and USB peripherals.

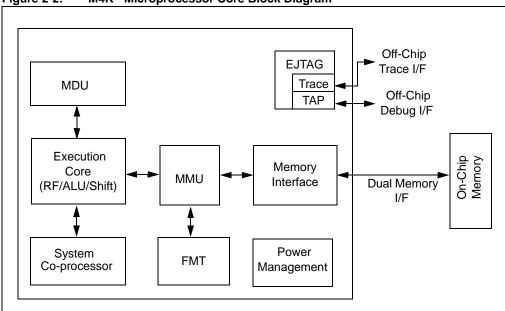

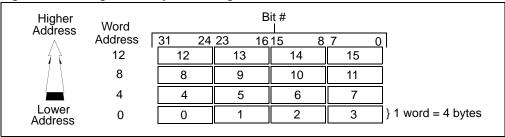

The M4K<sup>®</sup> CPU core is the heart of some PIC32 MCUs. The CPU performs operations under program control. Instructions are fetched by the CPU, decoded and executed synchronously. Instructions exist in either Program Flash memory or Data RAM memory.

The PIC32 CPU is based on a load/store architecture and performs most operations on a set of internal registers. Specific load and store instructions are used to move data between these internal registers and the outside world.

Figure 2-2: M4K<sup>®</sup> Microprocessor Core Block Diagram

# 2.2.1 Busses

There are two separate busses on PIC32 devices. One bus is responsible for the fetching of instructions to the CPU, and the other is the data path for load and store instructions. Both the instruction, or I-side bus, and the data, or D-side bus, are connected to the bus matrix unit. The bus matrix is a switch that allows multiple accesses to occur concurrently in a system. The bus matrix allows simultaneous accesses between different bus masters that are not attempting accesses to the same target. The bus matrix serializes accesses between different masters to the same target through an arbitration algorithm.

Since the CPU has two different data paths to the bus matrix, the CPU is effectively two different bus masters to the system. When running from Flash memory, load and store operations to SRAM and the internal peripherals will occur in parallel to instruction fetches from Flash memory.

In addition to the CPU, and depending on the device variant, there are other bus masters in PIC32 devices:

- DMA controller

- In-Circuit Debugger (ICD) unit

- USB controller

- · CAN controller

- · Ethernet controller

# 2.2.2 Introduction to the Programming Model

The PIC32 processor has the following features:

- · 5-stage pipeline

- · 32-bit Address and Data Paths

- DSP-like Multiply-add and multiply-subtract instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted multiply instruction (MUL)

- Zero and One detect instructions (CLZ, CLO)

- Wait instruction (WAIT)

- Conditional move instructions (MOVZ, MOVN)

- Implements MIPS32® Enhanced Architecture (Release 2)

- Vectored interrupts

- Programmable exception vector base

- · Atomic interrupt enable/disable

- · General Purpose Register (GPR) shadow sets

- · Bit field manipulation instructions

- MIPS16e® Application Specific Extension improves code density

- Special PC-relative instructions for efficient loading of addresses and constants

- Data type conversion instructions (ZEB, SEB, ZEH, SEH)

- · Compact jumps

- Stack frame set-up and tear-down SAVE and RESTORE macro instructions

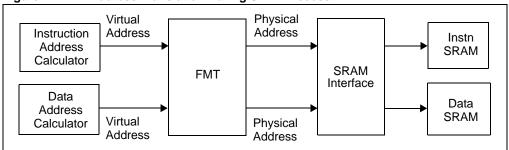

- Memory Management Unit with simple Fixed Mapping Translation (FMT)

- Processor to/from Coprocessor register data transfers

- Direct memory to/from Coprocessor register data transfers

- Performance-optimized Multiply-Divide Unit (High-performance build-time option)

- Maximum issue rate of one 32 x 16 multiply per clock

- Maximum issue rate of one 32 x 32 multiply every other clock

- Early-in divide control 11 to 34 clock latency

- Low-Power mode (triggered by WAIT instruction)

- Software breakpoints via the SDBBP instruction

#### 2.2.3 Core Timer

The PIC32 architecture includes a core timer that is available to application programs. This timer is implemented in the form of two co-processor registers: the Count register, and the Compare register. The Count register is incremented every two system clock (SYSCLK) cycles. The incrementing of Count can be optionally suspended during Debug mode. The Compare register is used to cause a timer interrupt if desired. An interrupt is generated when the Compare register matches the Count register. An interrupt is taken only if it is enabled in the Interrupt Controller module.

For more information on the core timer, see 2.12 "Coprocessor 0 (CP0) Registers" and Section 8. "Interrupts." (DS61108) in the "PIC32 Family Reference Manual".

#### 2.3 PIC32 CPU DETAILS

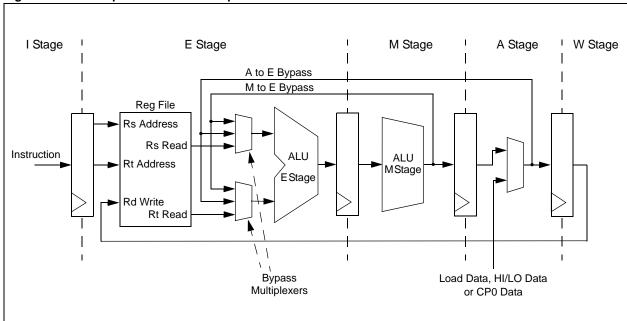

### 2.3.1 Pipeline Stages

The pipeline consists of five stages:

- Instruction (I) Stage

- · Execution (E) Stage

- · Memory (M) Stage

- Align (A) Stage

- · Writeback (W) Stage

#### 2.3.1.1 I STAGE - INSTRUCTION FETCH

#### During I stage:

- · An instruction is fetched from the instruction SRAM

- MIPS16e<sup>®</sup> instructions are converted into instructions that are similar to MIPS32<sup>®</sup> instructions

#### 2.3.1.2 E STAGE - EXECUTION

#### During E stage:

- Operands are fetched from the register file

- · Operands from the M and A stage are bypassed to this stage

- The Arithmetic Logic Unit (ALU) begins the arithmetic or logical operation for register-to-register instructions

- The ALU calculates the data virtual address for load and store instructions and the MMU performs the fixed virtual-to-physical address translation

- The ALU determines whether the branch condition is true and calculates the virtual branch target address for branch instructions

- Instruction logic selects an instruction address and the MMU performs the fixed virtual-to-physical address translation

- · All multiply divide operations begin in this stage

#### 2.3.1.3 M STAGE - MEMORY FETCH

#### During M stage:

- · The arithmetic or logic ALU operation completes

- The data SRAM access is performed for load and store instructions

- A 16 x 16 or 32 x 16 MUL operation completes in the array and stalls for one clock in the M stage to complete the carry-propagate-add in the M stage

- A 32 x 32 MUL operation stalls for two clocks in the M stage to complete the second cycle of the array and the carry-propagate-add in the M stage

- Multiply and divide calculations proceed in the MDU. If the calculation completes before the IU moves the instruction past the M stage, then the MDU holds the result in a temporary register until the IU moves the instructions to the A stage (and it is consequently known that it will not be killed).

#### 2.3.1.4 A STAGE - ALIGN

#### During A stage:

- A separate aligner aligns loaded data with its word boundary

- A MUL operation makes the result available for writeback. The actual register writeback is performed in the W stage

- From this stage, load data or a result from the MDU are available in the E stage for bypassing

# 2.3.1.5 W STAGE - WRITEBACK

During W stage:

For register-to-register or load instructions, the result is written back to the register file.

The M4K<sup>®</sup> Microprocessor core implements a "bypass" mechanism that allows the result of an operation to be sent directly to the instruction that needs it without having to write the result to the register, and then read it back.

Figure 2-3: Simplified PIC32 CPU Pipeline

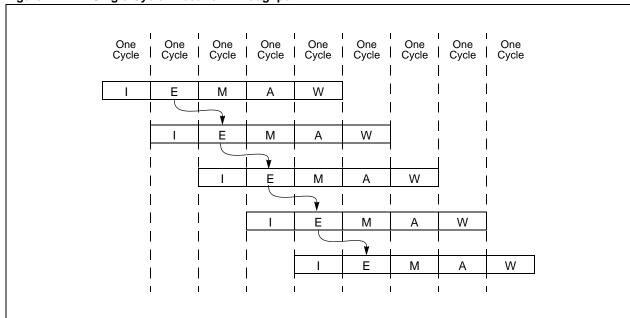

The results of using instruction pipelining in the PIC32 core is a fast, single-cycle instruction execution environment.

Figure 2-4: Single-Cycle Execution Throughput

#### 2.3.2 Execution Unit

The PIC32 Execution Unit is responsible for carrying out the processing of most of the instructions of the MIPS® instruction set. The Execution Unit provides single-cycle throughput for most instructions by means of pipelined execution. Pipelined execution, sometimes referred to as "pipelining", is where complex operations are broken into smaller pieces called stages. Operation stages are executed over multiple clock cycles.

The Execution Unit contains the following features:

- · 32-bit adder used for calculating the data address

- · Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- · Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- · Shifter and Store Aligner

#### 2.3.3 MDU

The Multiply/Divide unit performs multiply and divide operations. The MDU consists of a 32 x 16 multiplier, result-accumulation registers (HI and LO), multiply and divide state machines, and all multiplexers and control logic required to perform these functions. The high-performance, pipelined MDU supports execution of a 16 x 16 or 32 x 16 multiply operation every clock cycle;  $32 \times 32$  multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issue of back-to-back  $32 \times 32$  multiply operations. Divide operations are implemented with a simple 1 bit per clock iterative algorithm and require 35 clock cycles in worst case to complete. Early-in to the algorithm detects sign extension of the dividend, if it is actual size is 24, 16, or 8 bit. the divider will skip 7, 15, or 23 of the 32 iterations. An attempt to issue a subsequent MDU instruction while a divide is still active causes a pipeline stall until the divide operation is completed.

The M4K<sup>®</sup> Microprocessor core implements an additional multiply instruction, MUL, which specifies that lower 32-bits of the multiply result be placed in the register file instead of the HI/LO register pair. By avoiding the explicit move from LO (MFLO) instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased. Two instructions, multiply-add (MADD/MADDU) and multiply-subtract (MSUB/MSUBU), are used to perform the multiply-add and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD/MADDU and MSUB/MSUBU operations are commonly used in Digital Signal Processor (DSP) algorithms.

#### 2.3.4 Shadow Register Sets

The PIC32 processor implements a copy of the General Purpose Registers (GPR) for use by high-priority interrupts. This extra bank of registers is known as a shadow register set. When a high-priority interrupt occurs the processor automatically switches to the shadow register set without software intervention. This reduces overhead in the interrupt handler and reduces effective latency.

The shadow register set is controlled by registers located in the System Coprocessor (CP0) as well as the interrupt controller hardware located outside of the CPU core.

For more information on shadow register sets, see Section 8. "Interrupts" (DS61108).

# 2.3.5 Pipeline Interlock Handling

Smooth pipeline flow is interrupted when an instruction in a pipeline stage can not advance due to a data dependency or a similar external condition. Pipeline interruptions are handled entirely in hardware. These dependencies, are referred to as "interlocks". At each cycle, interlock conditions are checked for all active instructions. An instruction that depends on the result of a previous instruction is an example of an interlock condition.

In general, MIPS® processors support two types of hardware interlocks:

- Stalls These interlocks are resolved by halting the entire pipeline. All instructions currently

executing in each pipeline stage are affected by a stall

- Slips These interlocks allow one part of the pipeline to advance while another part of the pipeline is held static

In the PIC32 processor core, all interlocks are handled as slips. These slips are minimized by grabbing results from other pipeline stages by using a method called register bypassing, which is described below.

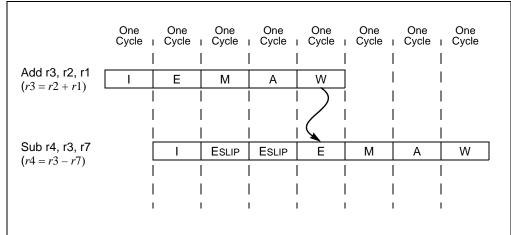

**Note:** To illustrate the concept of a pipeline slip, the following example is what would happen if the PIC32 core did not implement register bypassing.

As shown in Figure 2-5, the sub instruction has a source operand dependency on register r3 with the previous add instruction. The sub instruction slips by two clocks waiting until the result of the add is written back to register r3. This slipping does not occur on the PIC32 family of processors.

Figure 2-5: Pipeline Slip (If Bypassing Was Not Implemented)

# 2.3.6 Register Bypassing

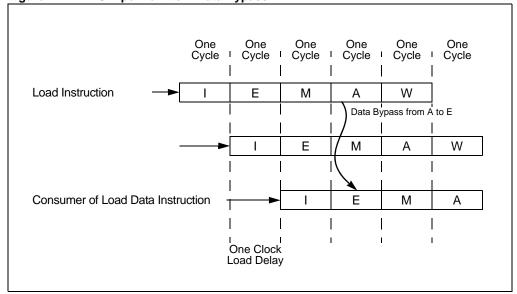

As mentioned previously, the PIC32 processor implements a mechanism called register bypassing that helps reduce pipeline slips during execution. When an instruction is in the E stage of the pipeline, the operands must be available for that instruction to continue. If an instruction has a source operand that is computed from another instruction in the execution pipeline, register bypassing allows a shortcut to get the source operands directly from the pipeline. An instruction in the E stage can retrieve a source operand from another instruction that is executing in either the M stage or the A stage of the pipeline. As seen in Figure 2-6, a sequence of three instructions with interdependencies does not slip at all during execution. This example uses both A to E, and M to E register bypassing. Figure 2-7 shows the operation of a load instruction utilizing A to E bypassing. Since the result of load instructions are not available until the A pipeline stage, M to E bypassing is not needed.

The performance benefit of register bypassing is that instruction throughput is increased to the rate of one instruction per clock for ALU operations, even in the presence of register dependencies.

One One One One One One Cycle Cycle Cycle Cycle Cycle Add₁ Ε W M Α r3 = r2 + r1M to E Bypass A to E Bypass Sub<sub>2</sub> Ε M W r4 = r3 - r7M to E Bypass Adda Ε M Α r5 = r3 + r4

Figure 2-6: IU Pipeline M to E Bypass

Figure 2-7: IU Pipeline A to E Data Bypass

# 2.4 SPECIAL CONSIDERATIONS WHEN WRITING TO CP0 REGISTERS

In general, the PIC32 core ensures that instructions are executed following a fully sequential program model. Each instruction in the program sees the results of the previous instruction. There are some deviations to this model. These deviations are referred to as "hazards".

In privileged software, there are two different types of hazards:

- Execution Hazards

- · Instruction Hazards

#### 2.4.0.1 EXECUTION HAZARDS

Execution hazards are those created by the execution of one instruction, and seen by the execution of another instruction. Table 2-1 lists execution hazards.

Table 2-1: Execution Hazards

| Created By   | Seen By                                                                                | Hazard On                                       | Spacing (Instructions) |

|--------------|----------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|

| MTC0         | Coprocessor instruction execution depends on the new value of the CU0 bit (Status<28>) | CU0 bit (Status<28>)                            | 1                      |

| MTC0         | ERET                                                                                   | EPC, DEPC, ErrorEPC                             | 1                      |

| MTC0         | ERET                                                                                   | Status                                          | 0                      |

| MTC0, EI, DI | Interrupted Instruction                                                                | IE bit (Status<0>)                              | 1                      |

| MTC0         | Interrupted Instruction                                                                | IP1 and IP0 bits<br>(Cause<1> and <0>)          | 3                      |

| MTC0         | RDPGPR, WRPGPR                                                                         | PSS<3:0> bits<br>(SRSCtl<9:6>)                  | 1                      |

| MTC0         | Instruction is not seeing a Core Timer interrupt                                       | Compare update that clears Core Timer Interrupt | 4                      |

| MTC0         | Instruction affected by change                                                         | Any other CP0 register                          | 2                      |

#### 2.4.0.2 INSTRUCTION HAZARDS

Instruction hazards are those created by the execution of one instruction, and seen by the instruction fetch of another instruction. Table 2-2 lists the instruction hazard.

Table 2-2: Instruction Hazards

| Created By | Seen By                                                                                                                   | Hazard On |

|------------|---------------------------------------------------------------------------------------------------------------------------|-----------|

| MTC0       | Instruction fetch seeing the new value (including a change to ERL followed by an instruction fetch from the useg segment) | Status    |

#### 2.5 ARCHITECTURE RELEASE 2 DETAILS

The PIC32 CPU utilizes Release 2 of the MIPS® 32-bit processor architecture, and implements the following Release 2 features:

· Vectored interrupts using and external-to-core interrupt controller:

Provide the ability to vector interrupts directly to a handler for that interrupt.

· Programmable exception vector base:

Allows the base address of the exception vectors to be moved for exceptions that occur when Status<sub>BEV</sub> is '0'. This allows any system to place the exception vectors in memory that is appropriate to the system environment.

• Atomic interrupt enable/disable:

Two instructions have been added to atomically enable or disable interrupts, and return the previous value of the Status register.

- The ability to disable the Count register for highly power-sensitive applications

- · GPR shadow registers:

Provides the addition of GPR shadow registers and the ability to bind these registers to a vectored interrupt or exception.

· Field, Rotate and Shuffle instructions:

Add additional capability in processing bit fields in registers.

· Explicit hazard management:

Provides a set of instructions to explicitly manage hazards, in place of the cycle-based SSNOP method of dealing with hazards.

#### 2.6 SPLIT CPU BUS

The PIC32 CPU core has two distinct busses to help improve system performance over a single-bus system. This improvement is achieved through parallelism. Load and store operations occur at the same time as instruction fetches. The two busses are known as the I-side bus which is used for feeding instructions into the CPU, and the D-side bus used for data transfers.

The CPU fetches instructions during the I pipeline stage. A fetch is issued to the I-side bus and is handled by the bus matrix unit. Depending on the address, the BMX will do one of the following:

- Forward the fetch request to the Prefetch Cache unit

- · Forward the fetch request to the DRM unit or

- · Cause an exception

Instruction fetches always use the I-side bus independent of the addresses being fetched. The BMX decides what action to perform for each fetch request based on the address and the values in the BMX registers. See 3.5 "Bus Matrix" in Section 3. "Memory Organization" (DS61115).

The D-side bus processes all load and store operations executed by the CPU. When a load or store instruction is executed the request is routed to the BMX by the D-side bus. This operation occurs during the M pipeline stage and is routed to one of several targets devices:

- Data Ram

- · Prefetch Cache/Flash Memory

- Fast Peripheral Bus (Interrupt controller, DMA, Debug unit, USB, Ethernet, GPIO Ports)

- General Peripheral Bus (UART, SPI, Flash Controller, EPMP/EPSP, RTCC Timers, Input Capture, PWM/Output Compare, ADC, Dual Compare, I<sup>2</sup>C, Clock, and Reset)

#### 2.7 INTERNAL SYSTEM BUSSES

The internal busses of the PIC32 processor connect the peripherals to the bus matrix unit. The bus matrix routes bus accesses from different initiators to a set of targets utilizing several data paths throughout the device to help eliminate performance bottlenecks.

Some of the paths that the bus matrix uses serve a dedicated purpose, while others are shared between several targets.

The data RAM and Flash memory read paths are dedicated paths, allowing low-latency access to the memory resources without being delayed by peripheral bus activity. The high-bandwidth peripherals are placed on a high-speed bus. These include the Interrupt controller, debug unit, DMA engine, the USB host/peripheral unit, and other high-bandwidth peripherals (i.e., CAN, Ethernet engines).

Peripherals that do not require high-bandwidth are located on a separate peripheral bus to save power.

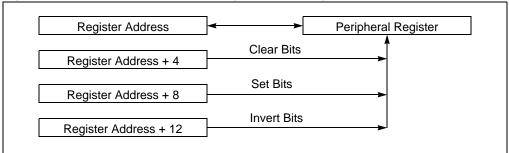

# 2.8 SET/CLEAR/INVERT

To provide single-cycle bit operations on peripherals, the registers in the peripheral units can be accessed in three different ways depending on peripheral addresses. Each register has four different addresses. Although the four different addresses appear as different registers, they are really just four different methods to address the same physical register.

Figure 2-8: Four Addresses for a Single Physical Register

The base register address provides normal Read/Write access, while the other three provide special write-only functions.

- Normal access

- · Set bit atomic RMW access

- Clear bit atomic RMW access

- Invert bit atomic RMW access

Peripheral reads must occur from the base address of each peripheral register. Reading from a Set/Clear/Invert address has an undefined meaning, and may be different for each peripheral.

Writing to the base address writes an entire value to the peripheral register. All bits are written. For example, assume a register contains 0xAAAA5555 before a write of 0x000000FF. After the write, the register will contain 0x000000FF (assuming that all bits are R/W bits).

Writing to the Set address for any peripheral register causes only the bits written as '1's to be set in the destination register. For example, assume that a register contains 0xAAAA5555 before a write of 0x000000FF to the set register address. After the write to the Set register address, the value of the peripheral register will contain 0xAAAA55FF.

Writing to the Clear address for any peripheral register causes only the bits written as '1's to be cleared to '0's in the destination register. For example, assume that a register contains 0xAAAA5555 before a write of 0x000000FF to the Clear register address. After the write to the Clear register address, the value of the peripheral register will contain 0xAAAA5500.

Writing to the Invert address for any peripheral register causes only the bits written as '1's to be inverted, or toggled, in the destination register. For example, assume that a register contains 0xAAAA5555 before a write of 0x000000FF to the invert register address. After the write to the Invert register, the value of the peripheral register will contain 0xAAAA55AA.

## 2.9 ALU STATUS BITS

Unlike most other PIC<sup>®</sup> microcontrollers, the PIC32 processor does not use Status register flags. Condition flags are used on many processors to help perform decision making operations during program execution. Flags are set based on the results of comparison operations or some arithmetic operations. Conditional branch instructions on these machines then make decisions based on the values of the single set of condition codes.

Instead, the PIC32 processor uses instructions that perform a comparison and stores a flag or value into a General Purpose Register. A conditional branch is then executed with this general purpose register used as an operand.

#### 2.10 INTERRUPT AND EXCEPTION MECHANISM

**Note:** Throughout this document, the terms "precise" and "imprecise" are used to describe exceptions. A precise exception is one in which the EPC (CP0, Register 14, Select 0) can be used to identify the instruction that caused the exception. For imprecise exceptions, the instruction that caused the exception cannot be identified. Most exceptions are precise. Bus error exceptions may be imprecise.

The PIC32 family of processors implement an efficient and flexible interrupt and exception handling mechanism. Interrupts and exceptions both behave similarly in that the current instruction flow is changed temporarily to execute special procedures to handle an interrupt or exception. The difference between the two is that interrupts are usually a result of normal operation, and exceptions are a result of error conditions such as bus errors.

When an interrupt or exception occurs, the processor does the following:

- The PC of the next instruction to execute after the handler returns is saved into a co-processor register.

- 2. Cause register is updated to reflect the reason for exception or interrupt.

- 3. Status register EXL or ERL bit is set to cause Kernel mode execution.

- 4. Handler PC is calculated from Ebase and SPACING values.

- 5. Processor starts execution from new PC.

This is a simplified overview of the interrupt and exception mechanism. See **Section 8.** "**Interrupts**" (DS61108) for more information regarding interrupt and exception handling.

## 2.11 PROGRAMMING MODEL

The PIC32 family of processors is designed to be used with a high-level language such as the C programming language. It supports several data types and uses simple but flexible addressing modes needed for a high-level language. There are 32 General Purpose Registers and two special registers for multiplying and dividing.

There are three different formats for the machine language instructions on the PIC32 processor:

- Immediate or I-type CPU instructions

- · Jump or J-type CPU instructions and

- · Registered or R-type CPU instructions

Most operations are performed in registers. The register type CPU instructions have three operands; two source operands and a destination operand.

Having three operands and a large register set allows assembly language programmers and compilers to use the CPU resources efficiently. This creates faster and smaller programs by allowing intermediate results to stay in registers rather than constantly moving data to and from memory.

The immediate format instructions have an immediate operand, a source operand and a destination operand. The jump instructions have a 26-bit relative instruction offset field that is used to calculate the jump destination.

#### 2.11.1 CPU Instruction Formats

A CPU instruction is a single 32-bit aligned word. The CPU instruction formats are:

- Immediate (see Figure 2-9)

- Jump (see Figure 2-10)

- Register (see Figure 2-11)

Table 2-3 describes the fields used in these instructions.

Table 2-3: CPU Instruction Format Fields

| Field       | Description                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| opcode      | 6-bit primary operation code.                                                                                                                                           |

| rd          | 5-bit specifier for the destination register.                                                                                                                           |

| rs          | 5-bit specifier for the source register.                                                                                                                                |

| rt          | 5-bit specifier for the target (source/destination) register or used to specify functions within the primary opcode REGIMM.                                             |

| immediate   | 16-bit signed immediate used for logical operands, arithmetic signed operands, load/store address byte offsets, and PC-relative branch signed instruction displacement. |

| instr_index | 26-bit index shifted left two bits to supply the low-order 28 bits of the jump target address.                                                                          |

| sa          | 5-bit shift amount.                                                                                                                                                     |

| function    | 6-bit function field used to specify functions within the primary opcode SPECIAL.                                                                                       |

#### Figure 2-9: Immediate (I-Type) CPU Instruction Format

| 31 26  | 25 21 | 20 16 | 15 0      |

|--------|-------|-------|-----------|

| opcode | rs    | rt    | immediate |

| 6      | 5     | 5     | 16        |

#### Figure 2-10: Jump (J-Type) CPU Instruction Format

|   | 31 2   | 26 25 | 21 20 | 16 15 | 11          | 10 6 | 5 | 0 |

|---|--------|-------|-------|-------|-------------|------|---|---|

|   | opcode |       |       |       | instr_index |      |   |   |

| _ | 6      |       |       |       | 26          |      |   |   |

# Figure 2-11: Register (R-Type) CPU Instruction Format

| 31 | 26     | 25 21 | 20 16 | 15 11 | 10 6 | 5 0      |

|----|--------|-------|-------|-------|------|----------|

|    | opcode | rs    | rt    | rd    | sa   | function |

|    | 6      | 5     | 5     | 5     | 5    | 6        |

#### 2.11.2 CPU Registers

The PIC32 architecture defines the following CPU registers:

- Thirty-two 32-bit General Purpose Registers (GPRs)

- Two special purpose registers to hold the results of integer multiply, divide, and multiply-accumulate operations (HI and LO)

- A special purpose program counter (PC), which is affected only indirectly by certain instructions; it is not an architecturally visible register

#### 2.11.2.1 CPU GENERAL PURPOSE REGISTERS

Two of the CPU General Purpose Registers have assigned functions:

- r0 This register is hard-wired to a value of '0', and can be used as the target register for any instruction the result of which will be discarded. r0 can also be used as a source when a '0' value is needed.

- r31 This is the destination register used by JAL, BLTZAL, BLTZALL, BGEZAL, and BGEZALL, without being explicitly specified in the instruction word; otherwise, r31 is used as a normal register

The remaining registers are available for general purpose use.

#### 2.11.2.2 REGISTER CONVENTIONS

Although most of the registers in the PIC32 architecture are designated as General Purpose Registers, as shown in Table 2-4, there are some recommended uses of the registers for correct software operation with high-level languages such as the Microchip C compiler.

Table 2-4: Register Conventions

|                 |                      | <del>-</del>                                                                                                  |  |  |

|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| CPU<br>Register | Symbolic<br>Register | Usage                                                                                                         |  |  |

| r0              | zero                 | Always '0' <sup>(1)</sup>                                                                                     |  |  |

| r1              | at                   | Assembler Temporary                                                                                           |  |  |

| r2 - r3         | v0-v1                | Function Return Values                                                                                        |  |  |

| r4 - r7         | a0-a3                | Function Arguments                                                                                            |  |  |

| r8 - r15        | t0-t7                | Temporary – Caller does not need to preserve contents                                                         |  |  |

| r16 - r23       | s0-s7                | Saved Temporary – Caller must preserve contents                                                               |  |  |

| r24 - r25       | t8-t9                | Temporary – Caller does not need to preserve contents                                                         |  |  |

| r26 - r27       | k0-k1                | Kernel temporary – Used for interrupt and exception handling                                                  |  |  |

| r28             | gp                   | Global Pointer – Used for fast-access common data                                                             |  |  |

| r29             | sp                   | Stack Pointer – Software stack                                                                                |  |  |

| r30             | s8 or fp             | Saved Temporary – Caller must preserve contents <i>OR</i> Frame Pointer – Pointer to procedure frame on stack |  |  |

| r31             | ra                   | Return Address <sup>(1)</sup>                                                                                 |  |  |

Note 1: Hardware enforced, not just convention.

#### 2.11.2.3 CPU SPECIAL PURPOSE REGISTERS

The CPU contains three special purpose registers:

- PC Program Counter register

- HI Multiply and Divide register higher result

- LO Multiply and Divide register lower result:

- During a multiply operation, the HI and LO registers store the product of integer multiply

- During a multiply-add or multiply-subtract operation, the HI and LO registers store the result of the integer multiply-add or multiply-subtract

- During a division, the HI and LO registers store the quotient (in LO) and remainder (in HI) of integer divide

- During a multiply-accumulate, the HI and LO registers store the accumulated result of the operation

Figure 2-12 shows the layout of the CPU registers.

Figure 2-12: CPU Registers

| re 2-12: | CPU Registers          |    |      |                 |        |

|----------|------------------------|----|------|-----------------|--------|

| 31       |                        | 0  | 31   |                 | 0      |

|          | r0 (zero)              |    |      | HI              |        |

|          | r1 (at)                |    |      | LO              |        |

|          | r2 (v0)                |    |      |                 |        |

|          | r3 (v1)                |    |      |                 |        |

|          | r4 (a0)                |    |      |                 |        |

|          | r5 (a1)                |    |      |                 |        |

|          | r6 (a2)                |    |      |                 |        |

|          | r7 (a3)                |    |      |                 |        |

|          | r8 (t0)                |    |      |                 |        |

|          | r9 (t1)                |    |      |                 |        |

|          | r10 (t2)               |    |      |                 |        |

|          | r11 (t3)               |    |      |                 |        |

|          | r12 (t4)               |    |      |                 |        |

|          | r13 (t5)               |    |      |                 |        |

|          | r14 (t6)               |    |      |                 |        |

|          | r15 (t7)               |    |      |                 |        |

|          | r16 (s0)               |    |      |                 |        |

|          | r17 (s1)               |    |      |                 |        |

|          | r18 (s2)               |    |      |                 |        |

|          | r19 (s3)               |    |      |                 |        |

|          | r20 (s4)               |    |      |                 |        |

|          | r21 (s5)               |    |      |                 |        |

|          | r22 (s6)               |    |      |                 |        |

|          | r23 (s7)               |    |      |                 |        |

|          | r24 (t8)               |    |      |                 |        |

|          | r25 (t9)               |    |      |                 |        |

|          | r26 (k0)               |    |      |                 |        |

|          | r27 (k1)               |    |      |                 |        |

|          | r28 (gp)               |    |      |                 |        |

|          | r29 (sp)               |    |      |                 |        |

|          | r30 (s8 or fp)         |    | 31   |                 | 0      |

|          | r31 (ra)               |    |      | PC              |        |

| Gei      | neral Purpose Register | 'S | Spec | ial Purpose Reg | isters |

Table 2-5: MIPS16e<sup>®</sup> Register Usage

| MIPS16e <sup>®</sup><br>Register<br>Encoding | 32-bit MIPS <sup>®</sup> Register Encoding | Symbolic<br>Name | Description                                                                                                                     |  |

|----------------------------------------------|--------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 0                                            | 16                                         | s0               | General Purpose Register                                                                                                        |  |

| 1                                            | 17                                         | s1               | General Purpose Register                                                                                                        |  |

| 2                                            | 2                                          | v0               | General Purpose Register                                                                                                        |  |

| 3                                            | 3                                          | v1               | General Purpose Register                                                                                                        |  |

| 4                                            | 4                                          | a0               | General Purpose Register                                                                                                        |  |

| 5                                            | 5                                          | a1               | General Purpose Register                                                                                                        |  |

| 6                                            | 6                                          | a2               | General Purpose Register                                                                                                        |  |

| 7                                            | 7                                          | а3               | General Purpose Register                                                                                                        |  |

| N/A                                          | 24                                         | t8               | MIPS16e® Condition Code register; implicitly referenced by the BTEQZ, BTNEZ, CMP, CMPI, SLT, SLTU, SLTI, and SLTIU instructions |  |

| N/A                                          | 29                                         | sp               | Stack Pointer register                                                                                                          |  |

| N/A                                          | 31                                         | ra               | Return Address register                                                                                                         |  |

Table 2-6: MIPS16e<sup>®</sup> Special Registers

| Symbolic<br>Name Purpose |                                                                                       |  |  |

|--------------------------|---------------------------------------------------------------------------------------|--|--|

| PC                       | Program counter. The PC-relative instructions can access this register as an operand. |  |  |

| HI                       | Contains high-order word of multiply or divide result.                                |  |  |

| LO                       | Contains low-order word of multiply or divide result.                                 |  |  |

# 2.11.3 How to Implement Stack/MIPS® Calling Conventions

The PIC32 CPU does not have hardware stacks. Instead, the processor relies on software to provide this functionality. Since the hardware does not perform stack operations itself, a convention must exist for all software within a system to use the same mechanism. For example, a stack can grow either toward lower address, or grow toward higher addresses. If one piece of software assumes that the stack grows toward lower address, and calls a routine that assumes that the stack grows toward higher address, the stack would become corrupted.

Using a system-wide calling convention prevents this problem from occurring. The Microchip C compiler assumes the stack grows toward lower addresses.

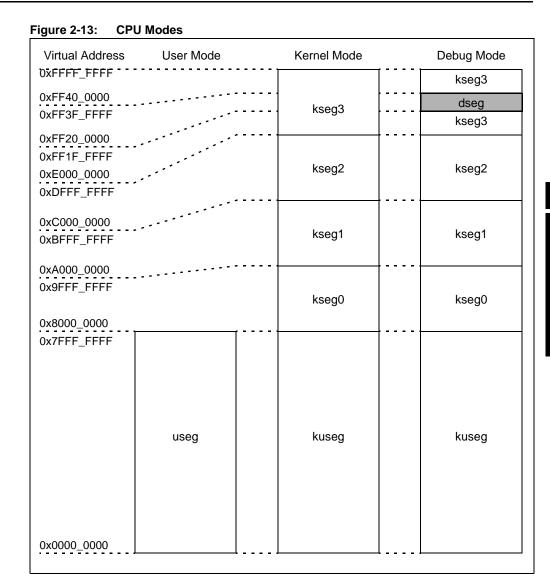

#### 2.11.4 Processor Modes

There are two operational modes and one special mode of execution in the PIC32 family CPUs; User mode, Kernel mode, and Debug mode. The processor starts execution in Kernel mode, and if desired, can stay in Kernel mode for normal operation. User mode is an optional mode that allows a system designer to partition code between privileged and unprivileged software. Debug mode is normally only used by a debugger or monitor.

One of the main differences between the modes of operation is the memory addresses that software is allowed to access. Peripherals are not accessible in User mode. Figure 2-13 shows the different memory maps for each mode. For more information on the processor's memory map, see **Section 3. "Memory Organization"** (DS61115).

#### 2.11.4.1 KERNEL MODE

In order to access many of the hardware resources, the processor must be operating in Kernel mode. Kernel mode gives software access to the entire address space of the processor as well as access to privileged instructions.

The processor operates in Kernel mode when the DM bit in the Debug register is '0' and the Status register contains one, or more, of the following values:

- UM = 0

- ERL = 1

- EXL = 1

When a non-debug exception is detected, EXL or ERL will be set and the processor will enter Kernel mode. At the end of the exception handler routine, an Exception Return (ERET) instruction is generally executed. The ERET instruction jumps to the Exception PC (EPC or ErrorPC depending on the exception), clears ERL, and clears EXL if ERL= 0.

If UM = 1 the processor will return to User mode after returning from the exception when ERL and EXL are cleared back to '0'.

#### 2.11.4.2 USER MODE

When executing in User mode, software is restricted to use a subset of the processor's resources. In many cases it is desirable to keep application-level code running in User mode where if an error occurs it can be contained and not be allowed to affect the Kernel mode code.

Applications can access Kernel mode functions through controlled interfaces such as the SYSCALL mechanism.

As seen in Figure 2-13, User mode software has access to the USEG memory area.

To operate in User mode, the Status register must contain each the following bit values:

- UM = 1

- EXL = 0

- ERL = 0

#### 2.11.4.3 DEBUG MODE

Debug mode is a special mode of the processor normally only used by debuggers and system monitors. Debug mode is entered through a debug exception and has access to all the Kernel mode resources as well as special hardware resources used to debug applications.

The processor is in Debug mode when the DM bit in the Debug register is '1'.

Debug mode is normally exited by executing a DERET instruction from the debug handler.

# 2.12 COPROCESSOR 0 (CP0) REGISTERS

The PIC32 uses a special register interface to communicate status and control information between system software and the CPU. This interface is called Coprocessor 0, or CP0. The features of the CPU that are visible through Coprocessor 0 are:

- · Core timer

- · Interrupt and exception control

- · Virtual memory configuration

- Shadow register set control

- · Processor identification

- · Debugger control

- Performance counters

System software accesses the registers in CP0 using coprocessor instructions such as MFC0 and MTC0. Table 2-7 describes the CP0 registers found on PIC32 devices.

Table 2-7: CP0 Registers

| Register<br>Number | Register Name | Function                                                                                        |  |  |

|--------------------|---------------|-------------------------------------------------------------------------------------------------|--|--|

| 0-6                | Reserved      | Reserved in the M4K <sup>®</sup> Microprocessor core.                                           |  |  |

| 7                  | HWREna        | Enables access via the RDHWR instruction to selected hardware registers in Non-privileged mode. |  |  |

| 8                  | BadVAddr      | Reports the address for the most recent address-related exception.                              |  |  |

| 9                  | Count         | Processor cycle count.                                                                          |  |  |

| 10                 | Reserved      | Reserved in the M4K <sup>®</sup> Microprocessor core.                                           |  |  |

| 11                 | Compare       | Core timer interrupt control.                                                                   |  |  |

| 12                 | Status        | Processor status and control.                                                                   |  |  |

|                    | IntCtl        | Interrupt control of vector spacing.                                                            |  |  |

|                    | SRSCtl        | Shadow register set control.                                                                    |  |  |

|                    | SRSMap        | Shadow register mapping control.                                                                |  |  |

| 13                 | Cause         | Describes the cause of the last exception.                                                      |  |  |

| 14                 | EPC           | Program counter at last exception.                                                              |  |  |

| 15                 | PRID          | Processor identification and revision                                                           |  |  |

|                    | Ebase         | Exception base address of exception vectors.                                                    |  |  |

| 16                 | Config        | Configuration register.                                                                         |  |  |

|                    | Config1       | Configuration register 1.                                                                       |  |  |

|                    | Config2       | Configuration register 2.                                                                       |  |  |

|                    | Config3       | Configuration register 3.                                                                       |  |  |

| 17-22              | Reserved      | Reserved in the M4K <sup>®</sup> Microprocessor core.                                           |  |  |

| 23                 | Debug         | Debug control/exception status.                                                                 |  |  |

|                    | TraceControl  | EJTAG trace control.                                                                            |  |  |

|                    | TraceControl2 | EJTAG trace control 2.                                                                          |  |  |

|                    | UserTraceData | User format type trace record trigger.                                                          |  |  |

|                    | TraceBPC      | Control tracing using an EJTAG Hardware breakpoint.                                             |  |  |

|                    | Debug2        | Debug control/exception status 1.                                                               |  |  |

| 24                 | DEPC          | Program counter at last debug exception.                                                        |  |  |

| 25-29              | Reserved      | Reserved in the M4K <sup>®</sup> Microprocessor core.                                           |  |  |

| 30                 | ErrorEPC      | Program counter at last error.                                                                  |  |  |

| 31                 | DeSAVE        | Debug handler scratchpad register.                                                              |  |  |

# 2.12.1 HWREna Register (CP0 Register 7, Select 0)

The HWREna register contains a bit mask that determines which hardware registers are accessible via the RDHWR instruction.

Register 2-1: HWREna: Hardware Accessibility Register; CP0 Register 7, Select 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | 1                 | _                 | _                 | -                 | -                 | 1                 | _                | _                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | -                 | _                 | _                 | _                 |                   | -                 | _                | -                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 | _                 |                   | MASK              | <3:0>            |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 Unimplemented: Read as '0'

bit 3-0 MASK<3:0>: Bit Mask bits

1 = Access is enabled to corresponding hardware register

0 = Access is disabled

Each of these bits enables access by the RDHWR instruction to a particular hardware register (which may not be an actual register). See the RDHWR instruction for a list of valid hardware registers.

# 2.12.2 BadVAddr Register (CP0 Register 8, Select 0)

BadVAddr is a read-only register that captures the most recent virtual address that caused an address error exception. Address errors are caused by executing load, store, or fetch operations from unaligned addresses, and also by trying to access Kernel mode addresses from User mode.

BadVAddr does not capture address information for bus errors, because they are not addressing errors.

Register 2-2: BadVAddr: Bad Virtual Address Register; CP0 Register 8, Select 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 31:24        |                   |                   |                   | BadVAddr          | <31:24>           |                   |                  |                  |

| 22.46        | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 23:16        |                   |                   |                   | BadVAddr          | <23:16>           |                   |                  |                  |

| 15:8         | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 15.6         | BadVAddr<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 7:0          |                   |                   |                   | BadVAdo           | lr<7:0>           |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 BadVAddr<31:0>: Bad Virtual Address bits

Captures the virtual address that caused the most recent address error exception.

# 2.12.3 Count Register (CP0 Register 9, Select 0)

The Count register acts as a timer, incrementing at a constant rate, whether or not an instruction is executed, retired, or any forward progress is made through the pipeline. The counter increments every other clock, if the DC bit in the Cause register is '0'.

Count can be written for functional or diagnostic purposes, including at Reset or to synchronize processors.

By writing the COUNTDM bit in the Debug register, it is possible to control whether Count continues to increment while the processor is in Debug mode.

Register 2-3: Count: Interval Counter Register; CP0 Register 9, Select 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31.24        |                   |                   |                   | COUNT<            | 31:24>            |                   |                  |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23.16        |                   |                   |                   | COUNT<            | 23:16>            |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | COUNT<15:8>       |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7.0          |                   |                   |                   | COUNT             | <7:0>             |                   |                  |                  |

| end |  |

|-----|--|

|     |  |

|     |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 COUNT<31:0>: Interval Counter bits

This value is incremented every other clock cycle.

# 2.12.4 Compare Register (CP0 Register 11, Select 0)

The Compare register acts in conjunction with the Count register to implement a timer and timer interrupt function. Compare maintains a stable value and does not change on its own.

When the value of Count equals the value of Compare, the CPU asserts an interrupt signal to the system interrupt controller. This signal will remain asserted until Compare is written.

Register 2-4: Compare: Interval Count Compare Register; CP0 Register 11, Select 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   | COMPARE           | <31:24>           |                   |                  |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23.10        |                   |                   |                   | COMPARE           | <23:16>           |                   |                  |                  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15.6         | COMPARE<15:8>     |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | COMPAR            | E<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 COMPARE<31:0>: Interval Count Compare Value bits

# 2.12.5 Status Register (CP0 Register 12, Select 0)

The read/write Status register contains the operating mode, interrupt enabling, and the diagnostic states of the processor. The bits of this register combine to create operating modes for the processor.

#### 2.12.5.1 INTERRUPT ENABLE

Interrupts are enabled when all of the following conditions are true:

- IE = 1

- EXL = 0

- ERL = 0

- DM = 0

If these conditions are met, the settings of the IPL bits enable the interrupts.

#### 2.12.5.2 OPERATING MODES

If the DM bit in the Debug register is '1', the processor is in Debug mode; otherwise, the processor is in either Kernel mode or User mode.

The CPU Status register bit settings shown in table determine User or Kernel mode:

Table 2-8: CPU Status Register Bits That Determine Processor Mode

| Mode                                                      |        | Bit/Setting    | I              |

|-----------------------------------------------------------|--------|----------------|----------------|

| User (requires all of the following bits and values)      | UM = 1 | EXL = 0        | <b>ERL</b> = 0 |

| Kernel (requires one or more of the following bit values) | UM = 0 | <b>EXL</b> = 1 | <b>ERL</b> = 1 |

**Note:** The Status register CU0 bit (Status<28>) control coprocessor accessibility. If any coprocessor is unusable, an instruction that accesses it generates an exception.

Register 2-5: Status: Status Register; CP0 Register 12, Select 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-x             | R/W-0 <sup>(1)</sup> | U-0               | R/W-x            | U-0              |

| 31:24        | _                 | _                 | _                 | CU0               | RP                   | _                 | RE               | _                |

| 00:40        | U-0               | R/W-1             | U-0               | R/W-1             | R/W-0                | U-0               | U-0              | U-0              |

| 23:16        | _                 | BEV               | _                 | SR                | NMI                  | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-x             | R/W-x                | R/W-x             | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 |                   | IPL<2:0>             |                   | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | R/W-x             | U-0                  | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   | _                 |                   | UM                |                      | ERL               | EXL              | ΙE               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28 CU0: Coprocessor 0 Usable bit

Controls access to Coprocessor 0

- 1 = Access allowed

- 0 = Access not allowed

Coprocessor 0 is always usable when the processor is running in Kernel mode, independent of the state of the CU0 bit.

# Register 2-5: Status: Status Register; CP0 Register 12, Select 0 (Continued)

bit 27 RP: Reduced Power bit

1 = Enables Reduced Power mode0 = Disables Reduced Power mode

bit 26 Unimplemented: Read as '0'

bit 25 RE: Reverse-endian Memory Reference Enable bit

Used to enable reverse-endian memory references while the processor is running in User mode

1 = User mode uses reversed endianness0 = User mode uses configured endianness

Debug, Kernel, or Supervisor mode references are not affected by the state of this bit.

bit 24-23 Unimplemented: Read as '0'

bit 22 BEV: Bootstrap Exception Vector Control bit

Controls the location of exception vectors.

1 = Bootstrap0 = Normal

bit 21 Unimplemented: Read as '0'

bit 20 SR: Soft Reset bit

Indicates that the entry through the Reset exception vector was due to a Soft Reset.

1 = Soft Reset; this bit is always set for any type of reset on the PIC32 core

0 = Not used on PIC32

Software can only write a '0' to this bit to clear it and cannot force a '0' to '1' transition.

bit 19 NMI: Non-Maskable Interrupt bit

Indicates that the entry through the reset exception vector was due to a NMI.

1 = NMI

0 = Not NMI (Soft Reset or Reset)

Software can only write a '0' to this bit to clear it and cannot force a '0' to '1' transition.

bit 18-13 Unimplemented: Read as '0'

bit 12-10 IPL<2:0>: Interrupt Priority Level bits

This bit is the encoded (0-7) value of the current IPL. An interrupt will be signaled only if the requested IPL is higher than this value.

bit 9-5 Unimplemented: Read as '0'

bit 4 UM: User Mode bit

This bit denotes the base operating mode of the processor. On the encoding of this bit is:

1 = Base mode is User mode

0 = Base mode in Kernel mode

The processor can also be in Kernel mode if ERL or EXL is set, regardless of the state of the UM bit.

bit 3 Unimplemented: Read as '0'

bit 2 ERL: Error Level bit

Set by the processor when a Reset, Soft Reset, NMI or Cache Error exception are taken.

1 = Error level

0 = Normal level

#### When ERL is set:

- · Processor is running in Kernel mode

- Interrupts are disabled

- ERET instruction will use the return address held in the ErrorEPC register instead of the EPC register

- Lower 2<sup>29</sup> bytes of kuseg are treated as an unmapped and uncached region. This allows main memory to be accessed in the presence of cache errors. The operation of the processor is undefined if the ERL bit is set while the processor is executing instructions from kuseg.

# **PIC32 Family Reference Manual**

#### Register 2-5: Status: Status Register; CP0 Register 12, Select 0 (Continued)

bit 1 **EXL:** Exception Level bit

Set by the processor when any exception other than Reset, Soft Reset, or NMI exceptions is taken.

1 = Exception level0 = Normal level

#### When EXL is set:

- Processor is running in Kernel mode

- · Interrupts are disabled

EPC, BD, and SRSCtl will not be updated if another exception is taken.

bit 0 **IE:** Interrupt Enable bit

Acts as the master enable for software and hardware interrupts:

1 = Interrupts are enabled0 = Interrupts are disabled

This bit may be modified separately via the DI and EI instructions

# 2.12.6 IntCtl: Interrupt Control Register (CP0 Register 12, Select 1)

The IntCtl register controls the vector spacing of the PIC32 architecture.

Register 2-6: IntCtl: Interrupt Control Register; CP0 Register 12, Select 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 |                   | _                 | _                 | _                | _                |

| 23:16        | U=0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 |                   | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | VS<              | 4:4>             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7.0          |                   | VS<2:0>           |                   | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-10 **Unimplemented:** Read as '0'

bit 9-5 **VS<4:0>:** Vector Spacing bits

These bits specify the spacing between each interrupt vector.

| Encoding | Spacing Between Vectors (hex) | Spacing Between Vectors (decimal) |

|----------|-------------------------------|-----------------------------------|

| 0x00     | 0x000 0x                      | 0                                 |

| 0x01     | 0x020                         | 32                                |

| 0x02     | 0x040                         | 64                                |

| 0x04     | 0x080                         | 128                               |

| 0x08     | 0x100                         | 256                               |

| 0x10     | 0x200                         | 512                               |

All other values are reserved. The operation of the processor is undefined if a reserved value is written to these bits.

bit 4-0 Unimplemented: Read as '0'

# 2.12.7 SRSCtl Register (CP0 Register 12, Select 2)

The SRSCtl register controls the operation of GPR shadow sets in the processor.

Table 2-9: Sources for New CSS on an Exception or Interrupt

| Exception Type         | Bit Source | Condition                                                | Comment                                  |

|------------------------|------------|----------------------------------------------------------|------------------------------------------|

| Exception              | ESS        | All                                                      | _                                        |

| Non-Vectored Interrupt | ESS        | IV bit = 0 (Cause<23>)                                   | Treat as exception                       |

| Vectored EIC Interrupt |            | IV bit = 1 (Cause<23>) and,<br>VEIC bit = 1 (Config3<6>) | Source is external interrupt controller. |

Register 2-7: SRSCtl: Shadow Register Set Register; CP0 Register 12, Select 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | R-0               | R-0               | R-0               | R-1               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | HSS.              | _                 | _                 |                  |                  |

| 22.46        | U-0               | U-0               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |