特殊機能レジスタ(SFR)

特殊機能レジスタ(SFR)はCPUの機能動作や、周辺デバイスの機能、動作を指定するためのレジスタ群です。以下がSFRを分類した表です。

(「PIC32MX1XX2XX-28-36-44-PIN-DS60001168K.pdf TABLE 4-1: SFR MEMORY MAP」より)

| Peripheral | Virtual Address | 備考 | |

|---|---|---|---|

| Base | Offset Start | ||

| Watchdog Timer | 0xBF80 | 0x0000 | |

| RTCC | 0x0200 | ||

| Timer1-5 | 0x0600 | ||

| Input Capture 1-5 | 0x2000 | ||

| Output Compare 1-5 | 0x3000 | ||

| IC1 and IC2 | 0x5000 | ||

| SPI1 and SPI2 | 0x5800 | ||

| UART1 and UART2 | 0x6000 | ||

| PMP | 0x7000 | ||

| ADC | 0x9000 | ||

| CVREF | 0x9800 | ||

| Comparator | 0xA000 | ||

| CTMU | 0xA200 | ||

| Oscillator | 0xF000 | ||

| Device and Revision ID | 0xF220 | ||

| Peripheral Module Disable | 0xF240 | ||

| Flash Controller | 0xF400 | NVMCON,NVMKEY, | |

| Reset | 0xF600 | ||

| PPS | 0xFA04 | ||

| Interrupts | 0xBF88 | 0x1000 | |

| Bus Matrix | 0x2000 | ||

| DMA | 0x3000 | ||

| USB | 0x5050 | ||

| PORTA-PORTC | 0x6000 | ||

| Configuration | 0xBFC0 | 0x0BF0 | |

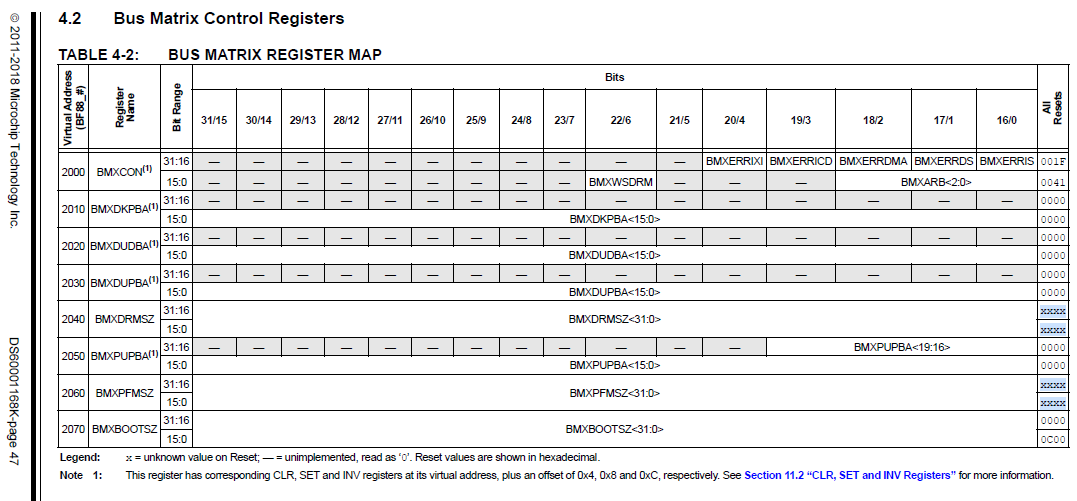

例えば、上記の「Bus Matrix」の レジスタ群は、次のようになっています。

このレジスタ群の設定で、RAMの一部にプログラムコードが配置できるようになります。( RAM をカーネルデータとカーネルプログラムに分割する)

以下にPIC32MX250F128B(データメモリ:32KB)において、8 Kをのカーネルデータ、残り24Kをプログラムに設定する例を示します。

(この場合、Kernel Program RAM Partition KSEG 0 24 KB は「0x80002000」から始まります。)

BMXDKPBA = 0x00002000;//8 KB のカーネルデータ (データRAM カーネルプログラム ベースアドレス レジスタ)

BMXDUDBA = 0x00008000;//24 KB のカーネルプログラム (データRAM ユーザデータベースアドレス レジスタ)

BMXDUPBA = 0x00008000;//ユーザデータのサイズ = 0、ユーザプログラムのサイズ = 0(データRAM ユーザプログラム ベースアドレス レジスタ)